You are hereOpenComRTOS Designer

OpenComRTOS Designer

OpenComRTOS Designer new support for ARC600, ARM-Cortex-R4 and ARM-Cortex-A9.

Altreonic has recently completed porting its OpenComRTOS Designer V.1.6 to new targets. The new ports illustrate again how with a single programming environment and small code size, OpenComRTOS Designer allows seamlessly connecting and supporting of low power ASIC cores, micro-controllers for safety critical applications and higher-end SoCs with multi-core processors with DSP and video processing capability. Contrary to many other solutions, OpenComRTOS allows to program multi/many-core in heterogenous configurations in a fully transparent way. Developers can remap Task and Interactions Entities (semaphores, FIFO, etc. called Hubs in OpenComRTOS) in a fully transparent way, with no changes to the source code. The underlying implementation is based on prioritised packet switching, an approach that is not only scalable, but also it provides real-time behaviour across any communication medium ranging from shared memory to long distance networks.

Rosetta landing Physics World 2014 Breakthrough of the Year

The Physics World, the member magazine of the Institute of Physics has nominated ESA's Rosetta mission as the 2014 Breakthrough of the Year for being the first to land a spacecraft on a comet.

Qualification Package for OpenComRTOS Designer v.1.6

28 October, 2014, Altreonic Linden Labs.

OpenComRTOS Designer is Altreonic’s formally developed network-centric RTOS with associated modeling and debugging tools. It is unique in the sense that it supports heterogeneous systems and hence it is much more a generic programming and modeling environment than a simple RTOS. While it supports high-end multicore processors, it also supports distributed systems, DSPs and small microcontrollers thanks to its very small code size and build-in support for transparent distributed real-time scheduling. Now available with a Qualification Pack for safety and mission critical applications.

Rosetta rendez-vous with comet. Virtuoso RTOS on board.

Historic mission in search of the Origin of the Solar System

With a go-ahead in 1993, the Rosetta ESA mission was finally launched in March 2004. After a 10 years journey through our solar system, it has finally arrived and made rendez-vous with the 67P/Churyumov-Gerasimenko Comet.

Meet up with Altreonic

Altreonic will be present at following events:

1. FISITA 2014 (Maastricht, 2-6 June 2014), the World Automotive Congress

2. The ESA Industry Space Days, taking place at ESTEC - Noordwijk, on June 3rd & 4th, 2014

3. ANTIFRAGILE 2014 workshop (Hasselt, 3rd June 2014)

Read further for details:

Integrated FPGA support with OpenComRTOS Designer

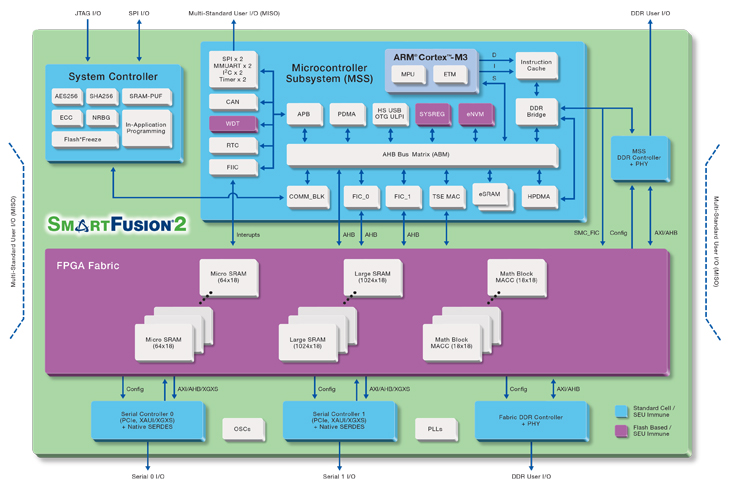

Altreonic announces integrated FPGA support for its multicore/manycore capable OpenComRTOS Designer on Microsemi’s SmartFusion-II.

Advanced chip technology has in the last decade reached a level of integration whereby complete systems can now be made available in a single package. Such Systems On a Chip (SoC) contains often multiple types of processor cores, each specialized for their function, but also smart I/O blocks, on chip networks, caches and program as well as data memory. Recent chips also add FPGA logic blocks.

Advanced chip technology has in the last decade reached a level of integration whereby complete systems can now be made available in a single package. Such Systems On a Chip (SoC) contains often multiple types of processor cores, each specialized for their function, but also smart I/O blocks, on chip networks, caches and program as well as data memory. Recent chips also add FPGA logic blocks.

Since 2005 Altreonic has developed a formally developed runtime system and development environment called OpenComRTOS Designer. Formally developed, it has a typical code size of 5 to 10 KB and supports systems in a fully scalable way. It transparently supports systems with heterogeneous processing nodes as well as heterogeneous communication mechanisms. This makes it suitable for networked, distributed systems as well as for on-chip many/multicore SoC. Board Support packages have been developed for example for TI’s C6678 8-core multi-DSP, Intel’s 48-core SCC as well as for multicore ARM and PPC systems, often replacing traditional memory hungry POSIX-style RTOS.

Today, Altreonic announces integrated FPGA support, demonstrated on Microsemi’s SmartFusion-II. On this chip the user finds a 166 MHz ARM Cortex M3, DMA, I/O blocks and memory as well as a flash programmable FPGA logic. Traditional approaches will treat the FPGA as a co-processing block that is explicitly accessed using dedicated software running on the ARM. In OpenComRTOS tasks synchronise and communicate using so-called intermediate “hub entities” that fully decouple tasks allowing them to be anywhere in the network whereby OpenComRTOS takes cares of the inter-node communication.

OpenComRTOS Designer new v.1.6 release

Altreonic has recently added new features to its network-centric RTOS that make programming systems with multiple, even heterogeneous processors even easier than before. The new support extend the virtual shared memory and virtual single processor support.

Supports system-wide shared data structures: virtual shared memory model

OpenComRTOS is the unique formally developed RTOS that can program seamlessly even heterogenous systems from a single processor to 1000's of processing nodes. It comes with a visual modeling environment whereby the developer independently specifies his parallel multi-processor target system and application architecture. Tasks and interaction entities can then be transparently mapped to any node in the system, even when the processors are of a different type. With prioritised scheduling and support for distributed priority inheritance, the system remains real time predictable with a typical code size of less than 10 KB per processing node. From v.1.6 of the OpenComRTOS Designer environment on, the developers benefits from a streamlined kernel source code and new features. OpenComRTOS Designer is however a lot more than an RTOS. Read further ....

Share |

New publication in the Gödel Series on real-time and many/multicore

Altreonic is pleased to release a new publication in its Gödel Series, entitled: "QoS and Real Time Requirements for Embedded Many- and Multicore Systems". While the first part is mainly a short summary on real-time scheduling, mostly Rate Monotonic Scheduling and Priority Inheritance support, it already establishes the jump to distributed real-time scheduling as supported in OpenComRTOS.

Altreonic is pleased to release a new publication in its Gödel Series, entitled: "QoS and Real Time Requirements for Embedded Many- and Multicore Systems". While the first part is mainly a short summary on real-time scheduling, mostly Rate Monotonic Scheduling and Priority Inheritance support, it already establishes the jump to distributed real-time scheduling as supported in OpenComRTOS.

Share |

The second part takes a closer look at modern advanced many/multi-core architectures, interrupt latency and inter-core communication measurements and makes the argument that the sharing of the on-chip resources, including the caches, makes it very hard to predict the temporal properties of an application. Rather than rejecting such advanced architectures, the argument is made to adapt the programming model to be able to handle the stochastic spread rather than trying to control it, even if a good design will try to minimise the spread.

Lastly, the bridge is made from Real-Time scheduling towards Quality of Service scheduling of on-chip resources. The connection is made with the specific case of Safety Integrity Levels. Finally, a proposal is made for a new concept that allows to classify components in terms of the assurance they provide for their functional requirements when resources are failing. Under the name ARRL (Assured Reliability and Resilience Level) it provides guidelines for selecting adequate architectures that allow to provide the required services in the presence of several classes of faults. This topic is the subject of on-going and future publications and provides the basis for extensions to the runtime support in OpenComRTOS.

The booklet if freely downloaded from Altreonic's website.

Altreonic HIRES2013 Workshop

Altreonic presents a working paper entitled:

"A Formalised Real-time Concurrent Programming Model for Scalable Parallel Programming",authors Eric Verhulst, Bernhard H.C. Sputh at the Workshop on High-performance and Real-time Embedded Systems(HiRES 2013) January 23, 2013, Berlin, Germany.

Held in conjunction with the 8th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC 2013)

Altreonic presents at MARC'ONERA'2012 Symposium in Toulouse

Altreonic has been presenting "Transparent Programming of Many/Multi Cores with OpenComRTOS. Comparing Intel 48-core SCC and TI 8-core TMS320C6678" at the Intel MARC symposium in Toulouse on Friday 20st July 2012. The symposium is focused on "bare metal programming" on the Intel experimental 48core SCC chip. In attachment the paper and presentation. For the full program, visit the ONERA website.