Trustworthy forever

Meet and share your views on ARRL with Altreonic

The ARRL (Assured Reliability and Resilience Level) criterion we presented a few weeks ago at the SASSUR/SAFECOMP workshop for the first time was generally well received and appreciated as a new way to look at safety and systems engineering. Of course, a new concept never emerges alone and also in the standards one can find approaches going in the same direction (SEooC, tool qualification, IMA, etc.). We also received very helpful critical remarks and we appreciate this as turning the ARRL criterion into a really usable and normative tool for engineering still requires serious thinking and refinement.

This process is on-going and you can meet and discuss with Altreonic at following upcoming events:

1. ADCSS workshop at ESTEC (Noordwijk)

The 7th ESA Workshop on Avionics Data, Control and Software Systems will take place from 22 till 24th October. This workshop discusses scientific as well as technical choices to be made to achieve a greater reuse of on-board electronics and software. Details can be found at the ESA website.

2. ICSSEA 2013 Conference (Paris)

Sponsored by AFIS (the French Association for Systems Engineering) and INCOSE, co-organized by TELECOM ParisTech, CS Communication & Systems, and the Génie Logiciel, the 25th edition of the ICSSEA Conference (International Conference on Software & Systems Engineering and their Applications) will be held in Paris on November 4-6, 2013. It aims at providing a critical survey of the status of tools, methods, and processes for elaborating software & systems. Details can be found at the ICSEEA website.

Dr. Bernhard Sputh of Altreonic will present "From safety integrity level to assured reliability and resilience level for composable safety critical systems".

3. IEEE ISSRE 2013 Symposium (Passedena)

The 24th IEEE International Symposium on Software Reliability Engineering will take place November 4-7 in Passadena, CA, USA. More details on the ISSRE website.

Eric Verhulst will present the ARRL criterion in the Industry Papers track.

Share |

Integrated FPGA support with OpenComRTOS Designer

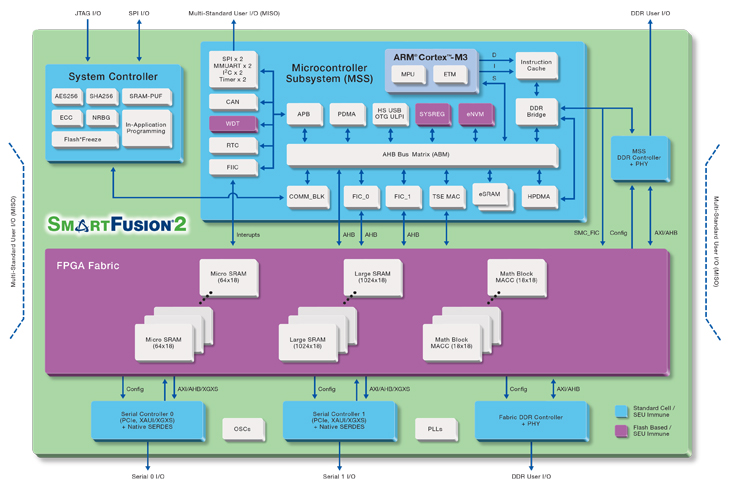

Altreonic announces integrated FPGA support for its multicore/manycore capable OpenComRTOS Designer on Microsemi’s SmartFusion-II.

Advanced chip technology has in the last decade reached a level of integration whereby complete systems can now be made available in a single package. Such Systems On a Chip (SoC) contains often multiple types of processor cores, each specialized for their function, but also smart I/O blocks, on chip networks, caches and program as well as data memory. Recent chips also add FPGA logic blocks.

Advanced chip technology has in the last decade reached a level of integration whereby complete systems can now be made available in a single package. Such Systems On a Chip (SoC) contains often multiple types of processor cores, each specialized for their function, but also smart I/O blocks, on chip networks, caches and program as well as data memory. Recent chips also add FPGA logic blocks.

Since 2005 Altreonic has developed a formally developed runtime system and development environment called OpenComRTOS Designer. Formally developed, it has a typical code size of 5 to 10 KB and supports systems in a fully scalable way. It transparently supports systems with heterogeneous processing nodes as well as heterogeneous communication mechanisms. This makes it suitable for networked, distributed systems as well as for on-chip many/multicore SoC. Board Support packages have been developed for example for TI’s C6678 8-core multi-DSP, Intel’s 48-core SCC as well as for multicore ARM and PPC systems, often replacing traditional memory hungry POSIX-style RTOS.

Today, Altreonic announces integrated FPGA support, demonstrated on Microsemi’s SmartFusion-II. On this chip the user finds a 166 MHz ARM Cortex M3, DMA, I/O blocks and memory as well as a flash programmable FPGA logic. Traditional approaches will treat the FPGA as a co-processing block that is explicitly accessed using dedicated software running on the ARM. In OpenComRTOS tasks synchronise and communicate using so-called intermediate “hub entities” that fully decouple tasks allowing them to be anywhere in the network whereby OpenComRTOS takes cares of the inter-node communication.

ARRL: a novel criterion for trustworthy safety critical systems

Altreonic will present the novel ARRL criterion at the SASSUR (Next Generation of System Assurance Approaches for Safety-Critical Systems) workshop of SAFECOMP2013 on 24th September in Toulouse, France. The paper is co-authored with the Simula Research Lab in Norway (Jose Luis de la Vara) and the University of Antwerp (Vincenzo di Florio).

In summary: ....

OpenComRTOS Designer new v.1.6 release

Altreonic has recently added new features to its network-centric RTOS that make programming systems with multiple, even heterogeneous processors even easier than before. The new support extend the virtual shared memory and virtual single processor support.

Supports system-wide shared data structures: virtual shared memory model

OpenComRTOS is the unique formally developed RTOS that can program seamlessly even heterogenous systems from a single processor to 1000's of processing nodes. It comes with a visual modeling environment whereby the developer independently specifies his parallel multi-processor target system and application architecture. Tasks and interaction entities can then be transparently mapped to any node in the system, even when the processors are of a different type. With prioritised scheduling and support for distributed priority inheritance, the system remains real time predictable with a typical code size of less than 10 KB per processing node. From v.1.6 of the OpenComRTOS Designer environment on, the developers benefits from a streamlined kernel source code and new features. OpenComRTOS Designer is however a lot more than an RTOS. Read further ....

Share |

New publication in the Gödel Series on real-time and many/multicore

Altreonic is pleased to release a new publication in its Gödel Series, entitled: "QoS and Real Time Requirements for Embedded Many- and Multicore Systems". While the first part is mainly a short summary on real-time scheduling, mostly Rate Monotonic Scheduling and Priority Inheritance support, it already establishes the jump to distributed real-time scheduling as supported in OpenComRTOS.

Altreonic is pleased to release a new publication in its Gödel Series, entitled: "QoS and Real Time Requirements for Embedded Many- and Multicore Systems". While the first part is mainly a short summary on real-time scheduling, mostly Rate Monotonic Scheduling and Priority Inheritance support, it already establishes the jump to distributed real-time scheduling as supported in OpenComRTOS.

Share |

The second part takes a closer look at modern advanced many/multi-core architectures, interrupt latency and inter-core communication measurements and makes the argument that the sharing of the on-chip resources, including the caches, makes it very hard to predict the temporal properties of an application. Rather than rejecting such advanced architectures, the argument is made to adapt the programming model to be able to handle the stochastic spread rather than trying to control it, even if a good design will try to minimise the spread.

Lastly, the bridge is made from Real-Time scheduling towards Quality of Service scheduling of on-chip resources. The connection is made with the specific case of Safety Integrity Levels. Finally, a proposal is made for a new concept that allows to classify components in terms of the assurance they provide for their functional requirements when resources are failing. Under the name ARRL (Assured Reliability and Resilience Level) it provides guidelines for selecting adequate architectures that allow to provide the required services in the presence of several classes of faults. This topic is the subject of on-going and future publications and provides the basis for extensions to the runtime support in OpenComRTOS.

The booklet if freely downloaded from Altreonic's website.

Meet Altreonic at TECHINNOV 2013 in Paris 14 February

Altreonic offers advanced embedded systems technology under a risk-free Open Technology License. The licensee receives all supporting design documents, formal models, source code, test suites, etc. and the right to rebrand the software whereby all certification and business risks are seriously reduced. Free yourself from legacy COTS and open source limitations. Two technologies are offered: the formally developed, network-centric OpenComRTOS Designer and the internet based GoedelWorks portal for supporting certifiable engineering projects.

Altreonic offre des technologies avancées pour systèmes embarqués sous une Licence de Technologie Ouverte sans risque. Le licencié reçoit tous les documents d'appui, les modèles formels, code source, des suites de tests, et le droit de renommer le logiciel. Tous les risques de certification et commerciaux sont sérieusement réduits. Libérez-vous des limites du COTS et source libre. Deux technologies sont proposées: OpenComRTOS Designer, un OS tmps réel distribué, formellement développé et le portail GoedelWorks pour soutenir des projets d'ingénierie certifiables.

Register for a B2B meeting here or contact us directly.

Altreonic HIRES2013 Workshop

Altreonic presents a working paper entitled:

"A Formalised Real-time Concurrent Programming Model for Scalable Parallel Programming",authors Eric Verhulst, Bernhard H.C. Sputh at the Workshop on High-performance and Real-time Embedded Systems(HiRES 2013) January 23, 2013, Berlin, Germany.

Held in conjunction with the 8th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC 2013)

Cross-domain systems and safety engineering: is it feasible?

Altreonic will be speaking at a seminar on Functional Safety in the Vehicle Industry organised by Flanders Drive presenting the results of the ASIL (“Automotive Safety Integrity Levels”) project.

The ASIL project created a development methodology for safety-critical systems, applicable to any type of vehicle or machine. Specialists involved will share the in-depth expertise acquired and illustrate this with various actual applications. The ASIL workflow was successfully imported in Altreonic's GoedelWorks portal where users can adapt it to integrate it with their own organisational processes.

The seminar focuses on the main challenges and opportunities associated with the systematic application of functional safety standards in system development and project management in the automotive industry. External experts as well as ASIL members will present relevant topics.

Eric Verhulst, CTO of Altreonic will speak of:

Cross-domain systems and safety engineering: is it feasible?

During the presentation, a new approach for developing composable systems with different SIL levels will be presented. It introduces the notion of ARRL (Assured Reliability and Resilience Level). See attached presentation.

Correctness-by-construction

Joseph Kiniry, Professor at the Technical University of Denmark, Copenhagen replied in a lively discussion topic on "GNATprove, integrating theorem provers with software development" in the LinkedIn discussion group "Formal Methods: Specification, Verification, TCG" as follows:

"We find Altreonic's work tremendous. Their pragmatic use of formal methods toward high-end business needs is really a case study in how to do things right and communicate ones results to industry and the academic community. We, too, believe that there is too much emphasis on post-design validation (and, rarely, verification) and believe that a pragmatic correctness-by-construction approach that appreciates and leverages existing quality development practices is the way forward." (quoted with permission).